# **Color Temperature and Ambient Light Sensor**

## Description

The SDF-DRGB-S2 device will perform color temperature measurement, brightness sensing. An internal state machine provides the ability to put the device into a low power state between color temperature measurement providing very low average power consumption.

#### **Features**

- •Color Temperature and Ambient Light Sensing

- -Low Power Management

- -I<sup>2</sup>C Fast Mode Interface Compatible

- -16 Bit resolution

- -IR blocking filters

- -Programmable Gain & Integration Time

- Power Management

- -Low Power 1uA Sleep State

- •I<sup>2</sup>C Interface Compatible

- -Up to 400kHz (I<sup>2</sup>C Fast Mode)

- -Device addr.: 7'b1000\_011

## **Applications**

- Brightness Sensing

- •Color Temperature Sensing

- ●Notebook

- Handheld device

- •Industrial and medical application

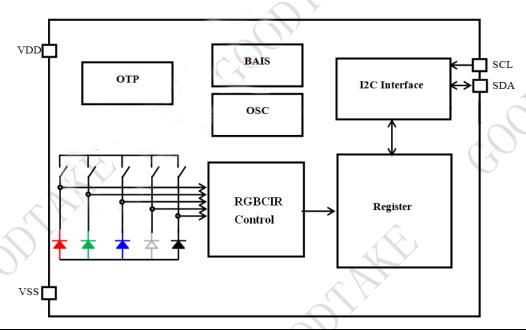

## Function Block Diagram

Rev1.0 8Nov2021

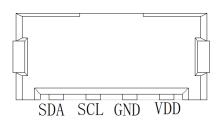

## Pin Description

| I/O TYPE | PIN NAME | DESCRIPTION                        |

|----------|----------|------------------------------------|

|          | VDD      | Digital/Analog Power Supply        |

| I        | SCL      | I <sup>2</sup> C serial clock line |

|          | GND      | Ground                             |

| I/O      | SDA      | I <sup>2</sup> C serial data line  |

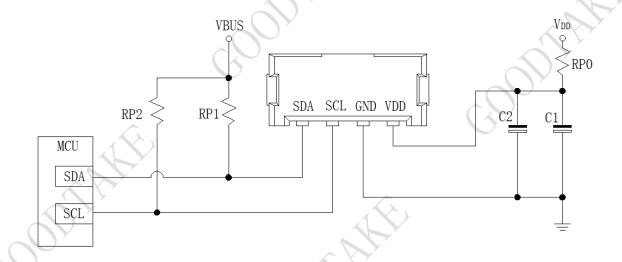

## **Typical Application Circuit**

**Application Circuit Design**

The pull-up resistors RP0 are required,  $200\Omega$  resistors can be used.

The capacitors (C1, C2) are required for power supply. The capacitors should be placed as close as possible to the device. The high frequency AC noises can be shunted to the ground by the capacitors. The transient current caused by digital circuit switching also can be handled by the capacitors. A typical value  $0.1 / 4.7 \mu F$  can be used.

The pull-up resistors (RP1, RP2) are required for  $I^2C$  communication. At fast speed mode (400kHz/s) and VBUS = 3V,  $1.5k\Omega$  resistors can be used.

## **GOODTAKE**

## **Absolute Maximum Ratings**

| SYMBOL | PARAMETER            | MIN  | MAX | UNIT       |

|--------|----------------------|------|-----|------------|

| VDD    | Power Supply Voltage | -0.5 | 3.6 | V          |

| Vin    | Input Voltage        | -0.5 | VDD | V          |

| Vout   | Output Voltage       | -0.5 | VDD | V          |

| Tj     | Junction Temperature | -40  | 85  | $^{\circ}$ |

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute- maximum-rated conditions for extended periods may affect device reliability.

Note 1: All voltage values are with respect to VSS.

# Recommended Operation Conditions

| SYMBOL | PARAMETER                     | MIN | TYP | MAX | UNIT       |

|--------|-------------------------------|-----|-----|-----|------------|

| VDD    | Power Supply Voltage          | 2.6 | 3.3 | 3.6 | V          |

| Vin    | Input Voltage                 | 0   |     | VDD | V          |

| Vout   | Output Voltage                | 0   |     | VDD | V          |

| TA     | Operating ambient temperature | -30 |     | 70  | $^{\circ}$ |

## Electrical Characteristics (VDD = 3.3V, Ta = 25°C)

| PARAMETER               | TEST<br>CONDITIONS                  | MIN      | TYP      | MAX        | UNIT |

|-------------------------|-------------------------------------|----------|----------|------------|------|

|                         | Active                              |          | 300      | 350        |      |

| Supply Current          | Sleep (@ADDR high)                  | <b>y</b> | 1        | 10         | uA   |

|                         | Sleep (@ADDR low)                   |          | 16       | 25         | uA   |

| SDA outputlow voltage   | 3mA sinkcurrent<br>6mA sink current | 0        |          | 0.4<br>0.6 | V    |

| LowLevel Input Voltage  |                                     |          |          | 0.6        | V    |

| HighLevel Input Voltage |                                     | VDD*0.7  | <u> </u> |            | V    |

## **Data Transmission Timing Requirements**

| PARAMETER                                    | CONDITIONS | MIN | MAX | UNIT |

|----------------------------------------------|------------|-----|-----|------|

| Output Low Level (SDA)                       | IOL = 4mA  |     | 0.5 | V    |

| SCL Operating Frequency                      |            |     | 400 | kHz  |

| Stop and Start Condition                     |            | 1.3 |     | us   |

| Hold Time After Repeated Start<br>Conditions |            | 0.6 | 9   | us   |

| SCL Clock Low Period                         |            | 1.3 |     | us   |

| SCL Clock High Period                        |            | 0.6 |     | us   |

| Repeated Start Condition Setup Time          |            | 0.6 |     | us   |

| Data Hold Time                               |            | 0   | 0.9 | us   |

| Data Setup Time                              |            | 100 |     | ns   |

| Clock/Data Fall Time                         |            |     | 300 | ns   |

| Clock/Data Rise Time                         |            |     | 300 | ns   |

| Stop Condition Setup Time                    |            | 0.6 |     | us   |

| PARAM                                        | ETER  | TEST CONDITIONS                                          | MIN | TYP   | MAX    | UNIT   |

|----------------------------------------------|-------|----------------------------------------------------------|-----|-------|--------|--------|

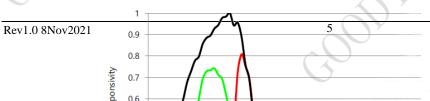

|                                              | R     |                                                          |     | 630   |        | nm     |

|                                              | G     |                                                          |     | 550   |        | nm     |

| Peak_<br>Sensitivity<br>Wavelength<br>of ADC | В     |                                                          |     | 480   |        | nm     |

|                                              | C     |                                                          |     | 590   |        | nm     |

|                                              | IR    |                                                          |     | 870   |        | nm     |

|                                              | R     |                                                          |     | 3730  |        | counts |

|                                              | G     | 3                                                        |     | 8635  |        | counts |

| Counter Value of ADC                         | В     | 5700K WLED,<br>1000Lux,Integration Time<br>10ms, AGAIN=1 |     | 7545  |        | counts |

| of ADC                                       | С     | Tollis, AGAIN=1                                          |     | 15830 |        | counts |

|                                              | IR    |                                                          |     | 50    |        | counts |

| Dark Count Value                             |       | Dark,Integration Time 100ms,<br>AGAIN=1                  | 0   | 3     | 6      | counts |

| ADC count Range                              |       |                                                          | 0   |       | 65,535 | counts |

|                                              |       | AGAIN = 0                                                |     | 1     |        |        |

|                                              | /     | AGAIN = 1                                                | 1   | 1.5   |        | X      |

| Gain sca                                     | aling | AGAIN = 2                                                |     | 2     |        | Λ      |

|                                              |       | AGAIN = 3                                                | > ' | 2.5   |        |        |

# Typical Performance Characteristics

### **Detailed Description**

#### Overview

The SDF-DRGB-S2 light-to-digital device provides on-chip RGBC and IR diodes, integrating amplifiers, ADCs, accumulators, clocks, buffers, comparators, a state machine and an I<sup>2</sup>C interface. Four integrating ADCs simultaneously convert the amplified photodiode currents into a digital value providing up to 16 bits of resolution.

The device connects to a video processor or image sensor through a standby I<sup>2</sup>C interface which supports up to 400-kbits/s data rate. The digital interface supports IO levels from 1.8V to 3.3V.

#### **Feature Description**

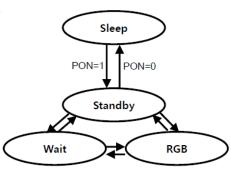

#### **System State machine**

The SDF-DRGB-S2 device provides ambient light and color temperature sensing. The internal state machine manages the operation of the device. It controls the RGB functionality and power down modes. Average power consumption is managed via control of variable endurance low power wait cycles. The advanced digital color light sensor portion of the SDF-DRGB-S2 contains a segmented circular photodiode array used for color measurements.

This architecture provides stable color sensing independent of the incident angle of light. Five integrating analog-to-digital converters (ADCs) integrate light energy from photodiodes simultaneously.

Communication with the device is accomplished through a fast (up to 400 kHz) two wire I<sup>2</sup>C serial bus for easy connection to a microcontroller or embedded controller. The device typically draws only 300uA in color operation and 1uA during power down.

< State machine >

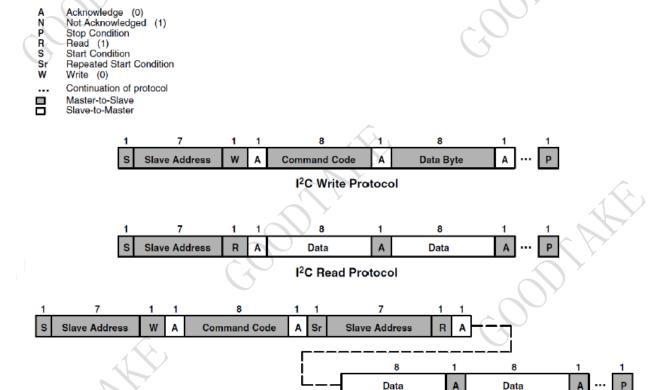

# Programming I<sup>2</sup>C Protocol

Interface and control of the SDF-DRGB-S2 is accomplished through an I<sup>2</sup>C serial compatible interface (standard or fast mode) to a set of registers that provide access to device control functions and output data. The device supports a selectable I<sup>2</sup>C address between b1000\_011 using 7-bit addressing protocol.

The I<sup>2</sup>C standard provides for three types of bus transaction: read, write, and a combined protocol. During a write operation, the first byte written is a command byte followed by data. In a combined protocol, the first byte written is the command byte followed by reading a series of bytes. If a read command is issued, the register address from the previous command will be used for data access.

I<sup>2</sup>C Protocol

# **GOODTAKE**

# SDF-DRGB-S2-TT/TR

| Addr | Bit7        | Bit6        | Bit5 | Bit4    | Bit3     | Bit2 | Bit1     | Bit0 | DEF  |

|------|-------------|-------------|------|---------|----------|------|----------|------|------|

| 0x80 |             | RESERVED    |      | DARK_EN | RESERVED | W_EN | RGB_EN   | PON  | 0x00 |

| 0x81 | IRGAIN AGA  |             |      | AIN     | W_TIME   |      | RGB_TIME |      | 0x00 |

| 0x82 |             |             |      | DEVI    | CE ID    |      |          |      | 0x24 |

| 0x83 |             | 7           |      | REVIS1  | ON ID    |      |          |      | 0x00 |

| 0xA0 |             |             |      | ADC_    | R[7:0]   |      |          |      | 0x00 |

| 0xA1 |             | ADC_R[15:8] |      |         |          |      |          |      | 0x00 |

| 0xA2 |             |             |      | ADC_    | G[7:0]   |      |          |      | 0x00 |

| 0xA3 |             |             |      | ADC_0   | G[15:8]  |      |          |      | 0x00 |

| 0xA4 |             |             |      | ADC_    | B[7:0]   |      |          |      | 0x00 |

| 0xA5 |             |             |      | ADC_I   | 3[15:8]  |      |          |      | 0x00 |

| 0xA6 |             | ADC_C[7:0]  |      |         |          |      |          |      | 0x00 |

| 0xA7 | ADC_C[15:8] |             |      |         |          |      |          |      | 0x00 |

| 0xA8 | ADC_IR[7:0  |             |      |         |          |      |          | 1    | 0x00 |

| 0xA9 |             |             | ()   | ADC_I   | R[15:8]  |      |          | ( )  | 0x00 |

Enable Register

| Addr | Bit7 | Bit6     | Bit5 | Bit4    | Bit3     | Bit2 | Bit1   | Bit0 | DEF  |

|------|------|----------|------|---------|----------|------|--------|------|------|

| 0x80 | ~    | RESERVED | )    | DARK_EN | RESERVED | W_EN | RGB_EN | PON  | 0x00 |

| FIELD   | BITS | DESCRIPTION                                                                                                                                                                                                                                                                                                                                           |

|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DARK_EN | 4    | Dark Offset cancellation Enable.                                                                                                                                                                                                                                                                                                                      |

| W_EN    | 2    | Wait State Enable.                                                                                                                                                                                                                                                                                                                                    |

| RGB_EN  | 1    | RGB, Clear and IR controller Enable.                                                                                                                                                                                                                                                                                                                  |

| PON     | 0    | Power ON. This bit activates the internal analog circuit to permit the timers and ADC channels to operate. Writing a 1 activates analog circuit. Writing a 0 disables analog circuit. During reads and writes over the I <sup>2</sup> C interface, this bit is temporarily overridden and analog circuit is enabled, independent of the state of PON. |

# Gain & Time control Register

| A  | ddr | Bit7 | Bit6 | Bit5 | Bit4 | Bit3   | Bit2 | Bit1     | Bit0 | DEF  |

|----|-----|------|------|------|------|--------|------|----------|------|------|

| 0) | x81 | IRG  | AIN  | AG.  | AIN  | W_TIME |      | RGB_TIME |      | 0x00 |

| FIELD    | BITS  | DESCRIPTION                                                                                        |  |

|----------|-------|----------------------------------------------------------------------------------------------------|--|

| IRGAIN   | [7:6] | IR Gain<br>0 : 1x, 1: 0.5x, 2: 0.25x, 3: 0.125x                                                    |  |

| AGAIN    | [5:4] | Analog Gain<br>0 : 1x, 1: 1.5x, 2: 2x, 3: 2.5x                                                     |  |

| W_TIME   | 3     | WAIT Time<br>0 : 10ms, 1: 100ms                                                                    |  |

| RGB_TIME | [2:0] | Optical Integration Time 0: 10ms, 1: 20ms, 2: 40ms, 3: 80ms 4: 100ms, 5: 200ms, 6: 400ms, 7: 800ms |  |

## ADC Data

| Addr | Bit7 Bit6   | Bit5 | Bit4  | Bit3    | Bit2 | Bit1 | Bit0 | DEF  |  |

|------|-------------|------|-------|---------|------|------|------|------|--|

| 0x82 | DEVICE ID   |      |       |         |      |      |      |      |  |

| 0x83 | REVISION ID |      |       |         |      |      |      |      |  |

| 0xA0 | ,           |      | ADC_  | _R[7:0] |      |      |      | 0x00 |  |

| 0xA1 |             |      | ADC_  | R[15:8] | ,    |      |      | 0x00 |  |

| 0xA2 |             |      | ADC_  | G[7:0]  |      |      |      | 0x00 |  |

| 0xA3 |             |      | ADC_0 | G[15:8] |      |      |      | 0x00 |  |

| 0xA4 |             |      | ADC_  | B[7:0]  |      |      |      | 0x00 |  |

| 0xA5 |             |      | ADC_  | B[15:8] |      |      |      | 0x00 |  |

| 0xA6 |             |      | ADC_  | _C[7:0] |      |      |      | 0x00 |  |

| 0xA7 | ADC_C[15:8] |      |       |         |      |      |      |      |  |

| 0xA8 | ADC_IR[7:0] |      |       |         |      |      |      |      |  |

| 0xA9 |             |      | ADC_I | R[15:8] |      |      |      | 0x00 |  |

| FIELD  | DESCRIPTION       |  |

|--------|-------------------|--|

| DEV_ID | Device ID (0x24)  |  |

| REV_ID | Revision ID (0x0) |  |

| ADC_R  | RED data          |  |

| ADC_G  | GREEN data        |  |

| ADC_B  | BLUE data         |  |

| ADC_C  | Clear data        |  |

| ADC_IR | IR data           |  |

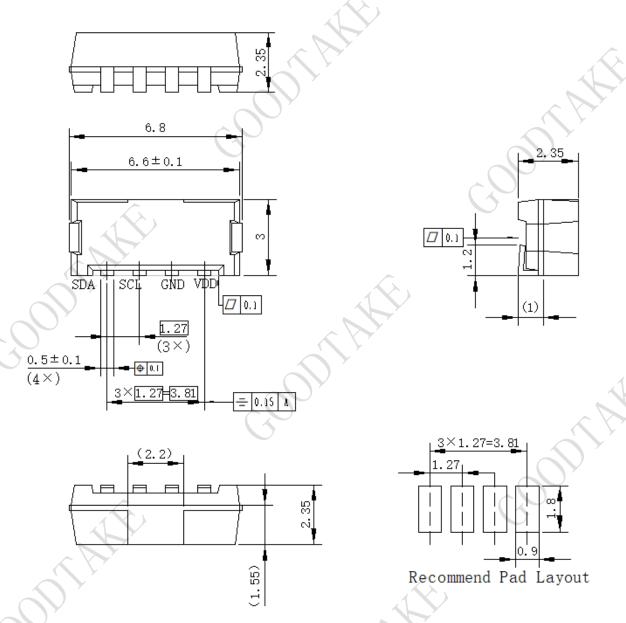

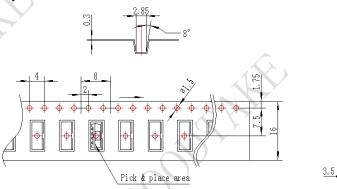

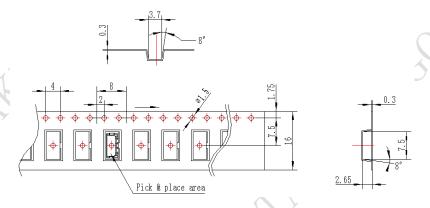

## Package Outline Dimensions

Notes: All dimensions are in millimeters. Tolerance is ±0.2 unless otherwise noted.

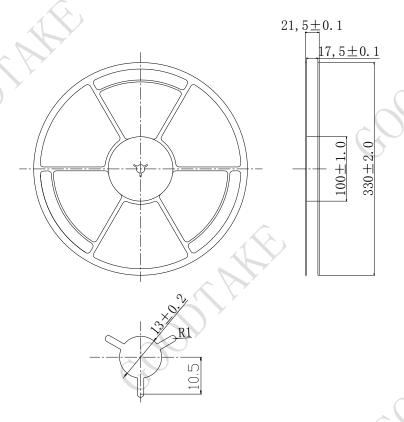

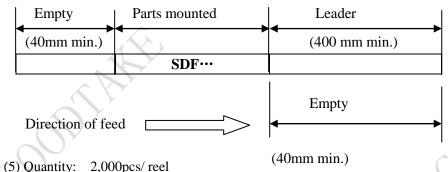

## TAPPING AND PACKING SPECIFICATIONS:

(1) Shape and dimensions of reels: unit in mm

(2) Dimensions of TR tape

(3) Dimensions of TT tape

(4) Configuration of tape

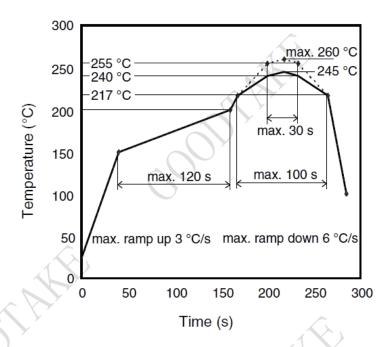

Reflow Soldering Profile

#### Antistatic Dry Pack

Opto devices in SMD package may be sensitive to moisture. Devices are taped & reeled, sealed in antistatic bag with silica gel desiccants.

Do not open the sealed moisture-proof bag before ready to use. If sealing is void, baking treatment may be required.

#### Storage

**Shelf life** – Devices should be stored in its original packing, in a controlled environment of temperature less than  $40 \, \text{C}$  and relative humidity below 90%.

Suggested shelf life is12 months in its original packing.

**Floor life** -72 hours in controlled environment, T<sub>amb</sub> <30 °C, RH <60%. Time between soldering and removing from moisture barrier bags must not exceed the time indicated in J-STD-020.

Moisture Sensitive Level classification: LEVEL 4

### Drying (Baking Process)

If original packing is voided (such as faded silica gel or exceeded storage time), baking treatment should be performed with the following conditions: T bake =  $40 + 5 \, \text{C}$ , RH <5%, Time =192hours.